New toolkit: Zynq support for Pothos Thu, Dec 18 2014 AM

After much work on the pothos-fpga toolkit, and investigations using the microzed, the work has been branched off and polished into its own toolkit called "pothos-zynq". This new toolkit contains zynq specific kernel drivers and zero-copy source and sink blocks that work with AXI DMA blocks inside the FPGA. The new pothos-zynq project page can be found here.

Pothos zero-copy/buffer integration

Counting the pothos-opencl toolkit, this is the second major project to make use of the Pothos buffer integration features. I was expecting to have to make changes to the buffer integration API, but the zynq support actually fit quite nicely. The managed buffer's "slab-index" was used here to identify pre-allocated DMA buffers used in the scatter gather table. When buffers are returned to the manager, this index provides immediate identification of the buffer (rather than using the buffers pointer, this is an O(1) operation).

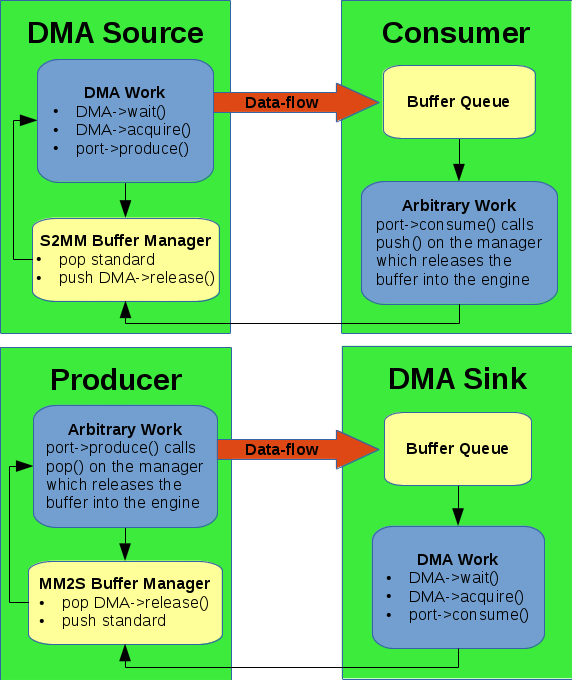

The following diagram identifies how the custom buffer manager and DMA source/sink work functions fit into a data flow to integrate with a generic consumer/producer block:

More info on the slab-index: The slab-index is used in the circular buffer implementation to preserve order. Blocks with filter history like FIR filters may use the circular buffer manager as an optimization to avoid memory copies.

New kernel module and userspace driver

We ended up creating own own kernel module for interfacing with the AXI DMA engine. There is a stock Xilinx provided module, as well as several custom implementations. With the idea in mind that Pothos is a userspace application, we created this userspace driver to operate almost completely in userspace with very little crossing into kernel space during operation. We actually only call into the kernel to initialize (DMA buffer allocations) and during runtime only to wait on interrupts.

This is a generally useful userspace driver and is not Pothos-specific in any way. It can also handle an arbitrary number of AXI DMA engines built into the FPGA. Check out the driver C interface here.

Loopback demonstration on the MicroZed

Zynq is a massive challenge to comprehend, let alone getting a working design on the FPGA, and integrating it with the ARM processors. Whats a device tree, FSBL, uImage, Vivados?... why are there so many files? Well, I cant make all that pain go away, but I did make an attempt to document getting a MicroZed Zynq evaluation board booting and running a loopback design so you can get the above code working and your project off the ground.

We document how to build every file and provide pre-built ones for the MicroZed (7020). If you have a different board, you should probably rebuild the files to get a working design. Check out the MicroZed loopback project here.

MicroZed board with hamster for scale:

More cool stuff on its way

- We will be adding channel support to the driver to share a DMA for multiple channels

- We will be working on integration with the stream interconnect in the pothos-fpga toolkit